Model Composer is a system-level modeling tool that facilitates FPGA hardware design. It extends Simulink® in many ways to provide a modeling environment that is well suited to hardware design. The tool provides high-level abstractions that are automatically compiled into an FPGA at the push of a button. The tool also provides access to underlying FPGA resources through low-level abstractions, allowing the construction of highly efficient FPGA designs.

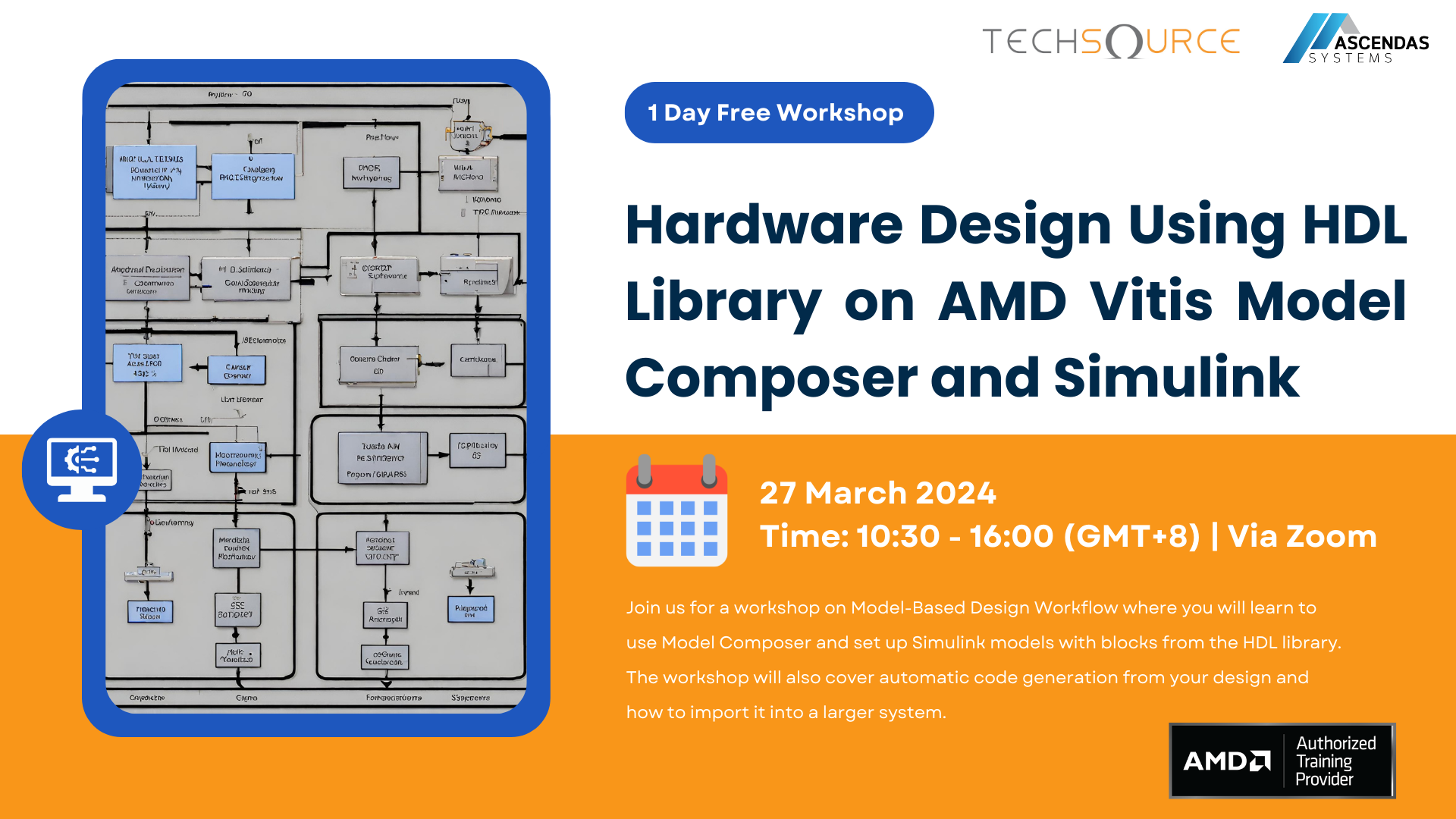

In this workshop, you will learn about the Model-Based Design workflow using Model Composer, how to setup the Simulink model using blocks from HDL library and do automatic code generation, how to import a Model Composer HDL design into a bigger system.

.png?width=200&height=212&name=MicrosoftTeams-image%20(111).png)

Dr.Marta Tjoa

Trainer and Senior Training Consultant

Dr Marta Tjoa is Trainer and Senior Training Consultant at TechSource Systems Pte Ltd. She has more than 25 years of experience in using MATLAB and Simulink and she has conducted numerous basic and advanced courses in MATLAB and Simulink to the industries in ASEAN countries. She has helped engineers, data scientists, and financial professionals, with little or no programming background to jumpstart MATLAB and Simulink in the shortest time. She helped them in doing some of their tasks on data modeling, data science analysis, system dynamic modeling, optimization and machine learning and deep learning for image processing application. She delivered courses to implement Digital Signal Processing and Image Processing applications on AMD FPGAs and SoCs using Simulink.

All rights reserved. Copyright © 2025 TechSource Systems and Ascendas Systems Group