The Ultimate Guide to Xilinx Training

Xilinx FPGA Design

Quick view

"Accelerating Applications with the Vitis Unified Software Environment"

Learn how to develop, debug, and profile new or existing C/C++ and RTL applications in the Vitis™ unified software environment targeting both data center (DC) and embedded applications. Also learn how to run designs on the Xilinx Alveo™ accelerator card using Nimbix Cloud.

-

Building a software application using the OpenCL™ API to run hardware kernels on Alveo accelerator cards.

-

Building a software application using the OpenCL API and the Linux-based Xilinx runtime (XRT) to schedule the hardware kernels and control data movement on an embedded processor platform.

-

Demonstrating the Vitis environment GUI flow and make file flow for both DC and embedded applications

-

Describing the Vitis platform execution model and XRT

-

Describing kernel development using C/C++ and RTL

-

Utilizing the Vitis analyzer tool to analyze reports

-

Explaining the design methodology to optimize a design

Enquire Now!!

Complete the form to get a quotation and consult with our sales representative.

COURSE DETAILS

Course Objective

Learn how to develop, debug, and profile new or existing C/C++ and RTL applications in the Vitis™ unified software environment targeting both data center (DC) and embedded applications. Also learn how to run designs on the Xilinx Alveo™ accelerator card using Nimbix Cloud.

Who should attend

Day 1

Vitis Tool Flow

▪ Introduction to the Vitis Unified Software Platform

Explains how software/hardware engineers and application developers can benefit from the Vitis unified software environment and OpenCL framework. {Lecture}

▪ Vitis IDE Tool Overview

Describes the elements of the development flow, such as software emulation, hardware emulation, and system run as well as debugging support for the host code and kernel code. {Lecture, Lab}

▪ Vitis Command Line Flow

Introduces the Vitis environment makefile flow where the user manages the compilation of host code and kernels. {Lecture, Lab}

Basic of Hardware Acceleration

▪ Introduction to Hardware Acceleration

Outlines the fundamental aspects of FPGAs, SoCs, and ACAPs that are required to guide the Vitis tool to the best computational architecture for any algorithm {Lecture}

Alveo Data Center Accelerator Cards

▪ Alveo Data Center Accelerator Cards Overview

Describes the Alveo Data Center accelerator cards and lists the advantages of these cards and the available software solutions stack. {Lecture}

▪ Alveo Accelerator Card Ecosystem Partner Solutions

Overview

Outlines the partner solutions available in the cloud and on premises for Alveo Data Center accelerator cards. {Lecture}

▪ Getting Started with Alveo Data Center Accelerator Cards

Describes the hardware and software installation procedures for the Alveo Data Center accelerator cards. {Lecture}

▪ Introduction to the Nimbix Cloud

Describes the Nimbix Cloud, the availability of the Alveo Data Center accelerator cards in the Nimbix Cloud, and how to run a design on the Nimbix Cloud. {Lecture}

Vitis Execution Model and XRT

▪ Vitis Execution Model and XRT

Describes the XRT and the OpenCL APIs used for such as setting up the platform, executing the target device and post-processing. {Lecture, Lab}

▪ Synchronization

Describes OpenCL synchronization techniques such as events, barriers, blocking write/read, and the benefit of using out-of-order execution. {Lecture, Lab}.

Day 2

NDRange (optional)

▪ Introduction to NDRanges

Explains the basics of NDRange (N dimensional range) and the OpenCL execution model that defines how kernels execute with the NDRange definition. {Lecture}

▪ Working with NDRanges

Outlines the host code and kernel code changes with respect to NDRange. Also explains how NDRange works and the best way to represent the work-group size for the FPGA architecture. {Lecture}

Design Analysis

▪ Profiling

Describes the different reports generated by the tool and how to view the reports that help to optimize data transfer and kernel optimization using the Vitis analyzer tool. {Lecture}

▪ Debugging

Explains the support for debugging host code and kernel code as well as tips to debug the system. {Lecture}

Kernel Development

▪ Introduction to C/C++ based Kernels

Describes the trade-offs between C/C++, OpenCL, and RTL applications and the benefits of C-based kernels. {Lecture, Lab}

▪ Using the RTL Kernel Wizard to Reuse Existing IP as Accelerators

Describes how the Vitis unified software development provides RTL kernel developers with a framework to integrate their hardware functions into an application running on a host PC connected to an FPGA via a PCIe® interface. {Lecture, Lab}

Optimization Methodology Guide

▪ Optimization Methodology

Describes the recommended flow for optimizing an application in the Vitis unified software development environment. {Lecture}

▪ C/C++ based Kernel Optimization

Reviews different techniques such as loop unrolling, pipelining, and DATAFLOW. {Lecture}

▪ Host Code Optimization

Describes the various optimization techniques such as reducing the overhead of kernel enqueing, and optimizing the data transfer between kernels and global memory. {Lecture}

▪ Optimizing the Performance of the Design

Describes the various optimization techniques such as optimizing the host code, data transfer between kernels and global memory and the kernel performance. {Lab} Libraries

▪ Vitis Accelerated Libraries

Reviews available libraries such as BLAS, Fintech, and OpenCV. The xfOpenCV library is a set of 60+ kernels, optimized for Xilinx FPGAs and SoCs, based on the OpenCV computer vision library. {Lecture}

Find the right Xilinx course for you

Xilinx FPGA Design

FPGA Design Expert

‘This course offers introductory training on the Vivado® Design Suite and demonstrates the FPGA design flow for those uninitiated to FPGA design. Read more>>

Xilinx FPGA Design

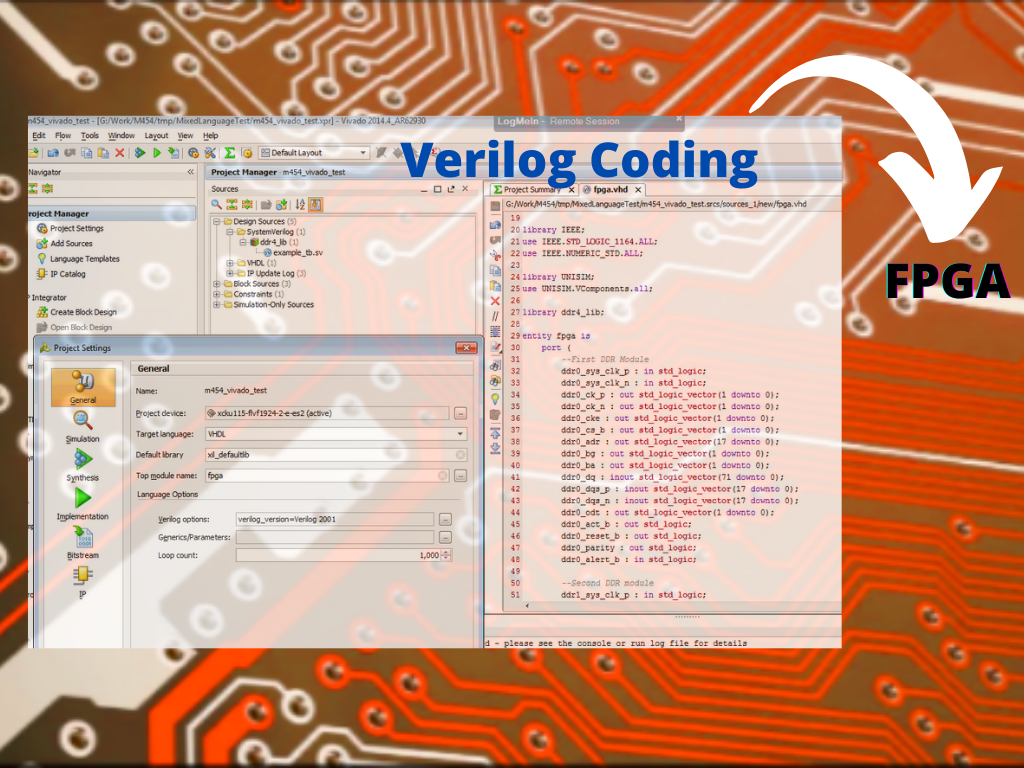

Verilog and FPGA Design Expert

‘Verilog & FPGA Design’ is a comprehensive training package that comprises of 2 course modules: Designing with Verilog and Essentials of FPGA. Based on Xilinx industry standard, this 6-day training package can be considered as the minimum training requirement for project readiness. Read more>>

Xilinx SOC and MPSOC

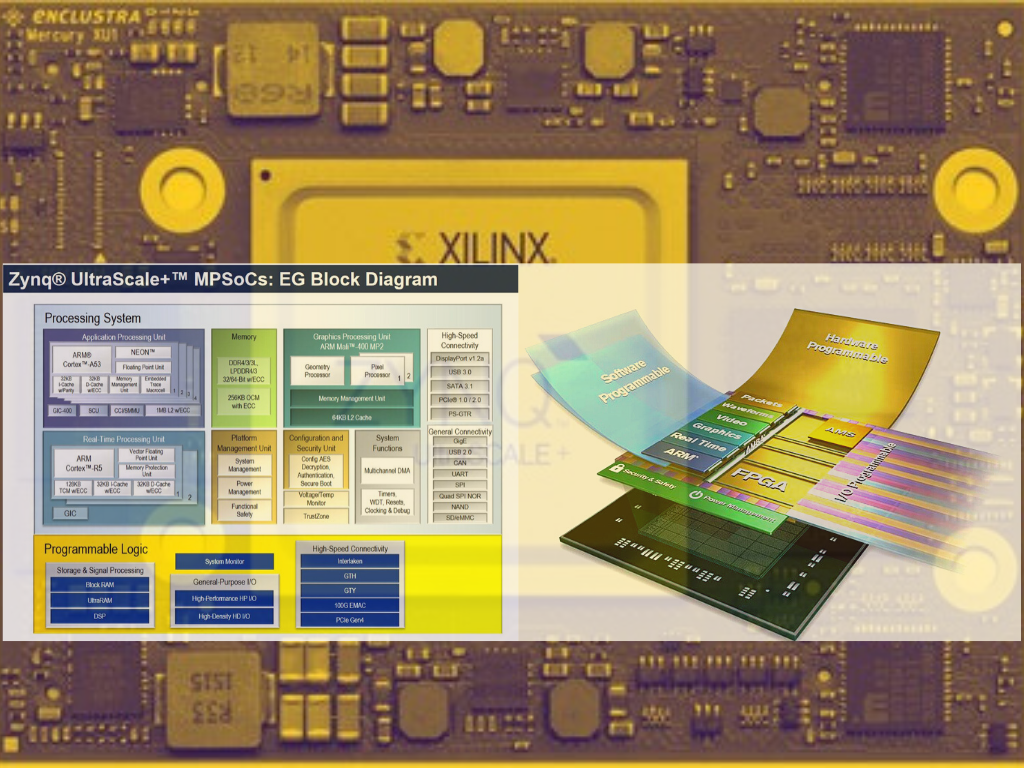

Zynq UltraScale+ MPSoC for the System Architect

Zynq® UltraScale+™ MPSoC devices provide 64-bit processor scalability while combining real-time control with soft and hard engines for graphics, video, waveform, and packet processing. Built on a common real-time processor and programmable logic equipped platform, three distinct variants include dual application processor (CG) devices, quad application processor and GPU (EG) devices, and video codec (EV) devices, creating unlimited possibilities for applications such as 5G Wireless, next generation ADAS, and Industrial Internet-of-Things. Read more>>

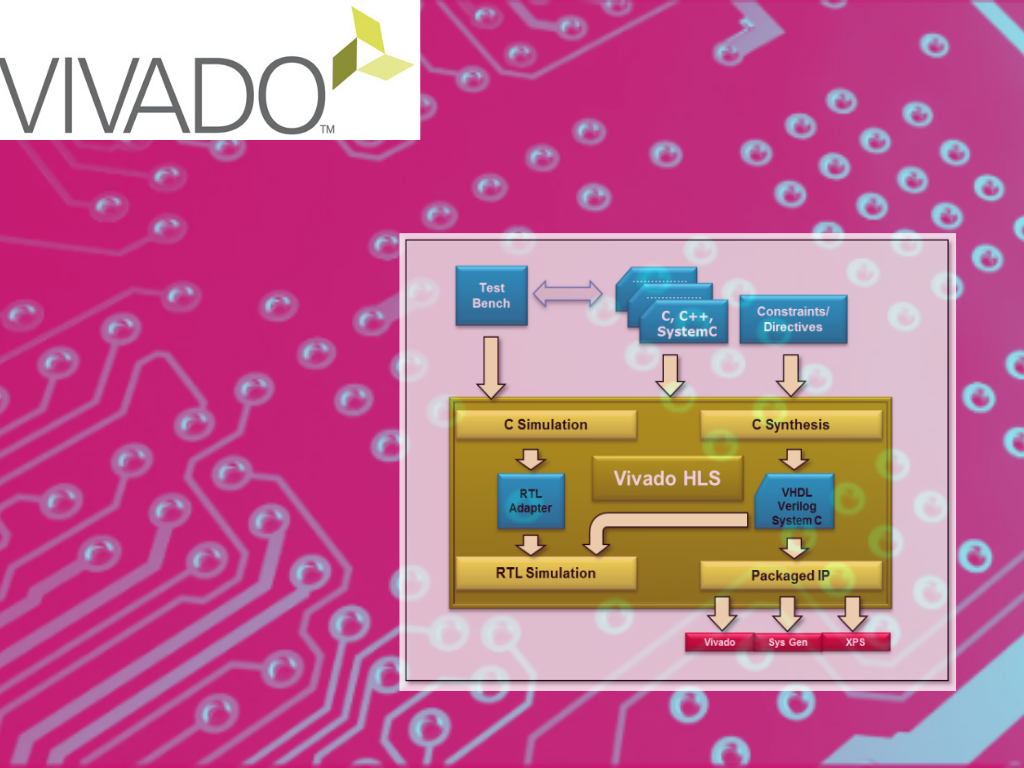

Xilinx Vivado / FPGA Design

Advanced Timing Closure Techniques for the Vivado Design Suite

Achieving repeatable and reliable timing is the designer’s ultimate goal. The task of writing timing constraints and validating the design against those constraints is commonly referred to as Timing Closure. This process is essential for every design. This course will provide experienced Vivado® Design Suite users with the skills to ensure that their designs work reliably over process, voltage, and temperature variations.